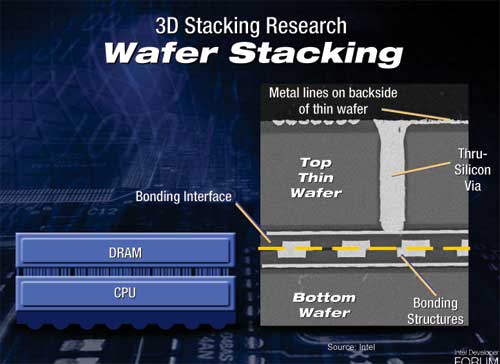

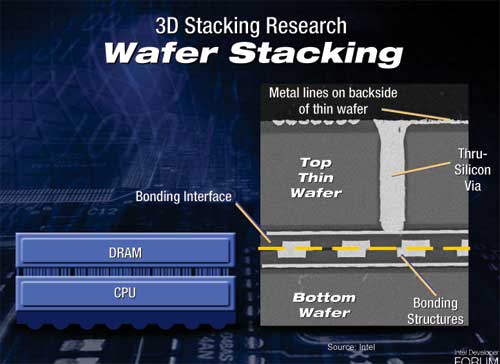

Wafer Stacking

I was reading some stuff that went on at IDF this past week. On the last day a guy was talking about trents and how things are going to many-core CPUs. That requires a lot of memory bandwidth, at that point CPUs become PIN limited. So why not stack Memory on top of the CPU, not cache, memory. Actually attaching a memory chip of some sort on top of your CPU chip and having thousands of connections straight to memory.

To do this though, Intel would have to follow in AMD's footsteps once more...onboard memory controllers.

This may never happen at all but I thought that was interesting.

First let's talk about wafer stacking; wafer stacking involves stacking two identically sized/shaped wafers on top of each other, and using through-silicon vias (interconnects) to connect the top wafer layer to the bottom layer. The best example of an application of this would be a DRAM wafer sitting on top of a CPU wafer, meaning that you would have memory (not cache, that would still be inside your CPU) sitting directly on top of your CPU.

With wafer stacking, instead of having hundreds or thousands of pins between your CPU and main memory, you have 1 - 10 million connections between your CPU and memory, directly increasing memory bandwidth. What's interesting is that this method of stacking could also mean the end of external memory.

To do this though, Intel would have to follow in AMD's footsteps once more...onboard memory controllers.

This may never happen at all but I thought that was interesting.

0

Comments

On the other hand, if I'm not mistaken some early computers had the math co-processor as a separate chip. I imagine folks grumbled when they combined the two, for the reason I mentioned above.

If it allowed prices to fall dramatically for the RAM/CPU package I could see it catching on.